TRANSFER-MOLD TYPE INSULATED TYPE

#### PS21869

#### INTEGRATED POWER FUNCTIONS

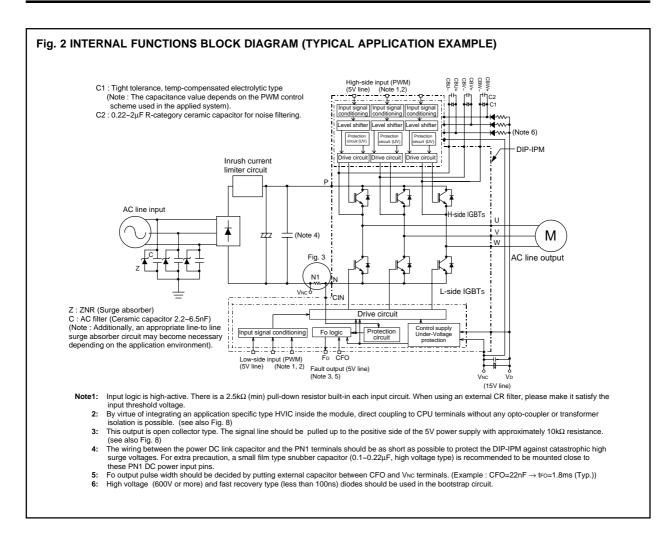

$600\mbox{V}/50\mbox{A}$  low-loss CSTBT inverter bridge for 3 phase DC-to-AC power conversion

#### INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS

- For upper-leg IGBTs: Drive circuit, High voltage isolated high-speed level shifting, Control supply under-voltage (UV) protection.

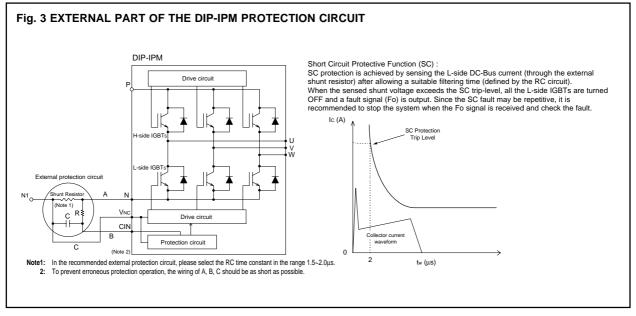

- For lower-leg IGBTs: Drive circuit, Control supply under-voltage protection (UV), Short circuit protection (SC). (Fig.3)

- Fault signaling: Corresponding to an SC fault (Lower-side IGBT) or a UV fault (Lower-side supply).

- Input interface: 5V line CMOS/TTL compatible. (High Active)

- UL Approved : Yellow Card No. E80276

### **APPLICATION**

AC100V~200V three-phase inverter drive for small power motor control.

# TRANSFER-MOLD TYPE INSULATED TYPE

# TRANSFER-MOLD TYPE INSULATED TYPE

# **MAXIMUM RATINGS** ( $T_j = 25^{\circ}C$ , unless otherwise noted)

#### **INVERTER PART**

| Symbol     | Parameter                          | Condition                | Ratings  | Unit |

|------------|------------------------------------|--------------------------|----------|------|

| Vcc        | Supply voltage                     | Applied between P-N      | 450      | V    |

| VCC(surge) | Supply voltage (surge)             | Applied between P-N      | 500      | V    |

| VCES       | Collector-emitter voltage          |                          | 600      | V    |

| ±lc        | Each IGBT collector current        | Tf = 25°C                | 50       | Α    |

| ±ICP       | Each IGBT collector current (peak) | Tf = 25°C, less than 1ms | 100      | Α    |

| Pc         | Collector dissipation              | Tf = 25°C, per 1 chip    | 70.4     | W    |

| Tj         | Junction temperature               | (Note 1)                 | -20~+125 | °C   |

Note 1 : The maximum junction temperature rating of the power chips integrated within the DIP-IPM is  $150^{\circ}$ C (@ Tf  $\leq 100^{\circ}$ C) however, to ensure safe operation of the DIP-IPM, the average junction temperature should be limited to Tj(ave)  $\leq 125^{\circ}$ C (@ Tf  $\leq 100^{\circ}$ C).

## **CONTROL (PROTECTION) PART**

| Symbol | Parameter                     | Condition                                       | Ratings     | Unit |

|--------|-------------------------------|-------------------------------------------------|-------------|------|

| VD     | Control supply voltage        | Applied between VP1-VPC, VN1-VNC                | 20          | V    |

| VDB    | Control supply voltage        | Applied between VUFB-VUFS, VVFB-VVFS, VWFB-VWFS | 20          | V    |

| VIN    | Input voltage                 | Applied between UP, VP, WP-VPC, UN, VN, WN-VNC  | -0.5~VD+0.5 | V    |

| VFO    | Fault output supply voltage   | Applied between Fo-VNC                          | -0.5~VD+0.5 | V    |

| IFO    | Fault output current          | Sink current at Fo terminal                     | 1           | mA   |

| Vsc    | Current sensing input voltage | Applied between CIN-VNC                         | -0.5~VD+0.5 | V    |

#### **TOTAL SYSTEM**

| Symbol    | Parameter                                                                  | Condition                                                                                                    | Ratings  | Unit |

|-----------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------|------|

| VCC(PROT) | Self protection supply voltage limit (short circuit protection capability) | $VD = 13.5 \sim 16.5 \text{V}$ , Inverter part $T_j = 125 ^{\circ}\text{C}$ , non-repetitive, less than 2 μs | 400      | V    |

| Tf        | Module case operation temperature                                          | (Note 2)                                                                                                     | -20~+100 | °C   |

| Tstg      | Storage temperature                                                        |                                                                                                              | -40~+125 | °C   |

| Viso      | Isolation voltage                                                          | 60Hz, Sinusoidal, AC 1 minute, connection pins to heat-sink plate                                            | 2500     | Vrms |

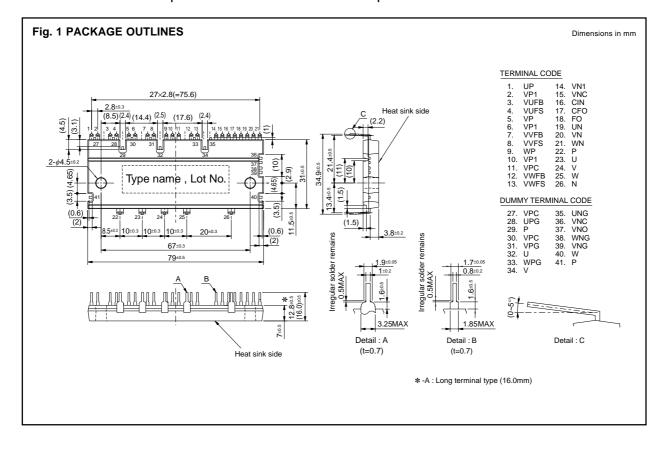

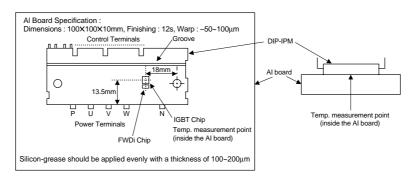

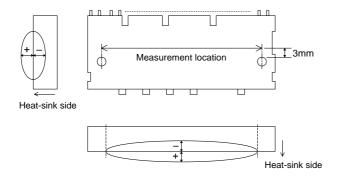

#### Note 2: Tf MEASUREMENT POINT

# TRANSFER-MOLD TYPE **INSULATED TYPE**

#### THERMAL RESISTANCE

| Symbol Parameter | Davamatar                | Condition                           | Limits |      |      | l lmit |

|------------------|--------------------------|-------------------------------------|--------|------|------|--------|

|                  | Condition                |                                     | Тур.   | Max. | Unit |        |

| Rth(j-f)Q        | Junction to case thermal | Inverter IGBT part (per 1/6 module) | _      | _    | 1.42 | °C/W   |

| Rth(j-f)F        | resistance (Note 3)      | Inverter FWDi part (per 1/6 module) | _      | _    | 2.00 | °C/W   |

$\textbf{Note 3:} \ \ \text{Grease with good thermal conductivity should be applied evenly with about +100} \\ \mu\text{m} \sim +200 \\ \mu\text{m on the contacting surface of DIP-IPM}$ and heat-sink.

# **ELECTRICAL CHARACTERISTICS** (Tj = 25°C, unless otherwise noted)

#### **INVERTER PART**

| Cumple of        | D-m-m-at-m                   | Condition                      |                                                                | Limits |      |      | Unit |  |

|------------------|------------------------------|--------------------------------|----------------------------------------------------------------|--------|------|------|------|--|

| Symbol           | Symbol Parameter             |                                | Condition                                                      |        | Тур. | Max. | Unit |  |

| VCE(cot)         | Collector-emitter saturation | VD = VDB = 15V                 | Ic = 50A, Tj = 25°C                                            | _      | 1.50 | 2.00 | `,,  |  |

| VCE(sat) voltage | VIN = 5V                     | Ic = 50A, Tj = 125°C           | _                                                              | 1.60   | 2.10 | V    |      |  |

| VEC              | FWDi forward voltage         | Tj = 25°C, -IC = 50A, VIN = 0V |                                                                | _      | 1.70 | 2.20 | V    |  |

| ton              |                              | Vcc = 300V, VD = VDB = 15V     |                                                                | 0.70   | 1.30 | 1.90 | μs   |  |

| trr              |                              |                                |                                                                | _      | 0.30 | _    | μs   |  |

| tc(on)           | Switching times              | IC = 50A, Tj = 125°C, VIN      | IC = 50A, T <sub>j</sub> = 125°C, VIN = $0 \leftrightarrow 5V$ |        | 0.40 | 0.60 | μs   |  |

| toff             |                              | Inductive load (upper-lov      | ver arm)                                                       | _      | 2.00 | 2.60 | μs   |  |

| tc(off)          |                              |                                |                                                                | _      | 0.65 | 0.90 | μs   |  |

| ICES             | Collector-emitter cut-off    |                                | Tj = 25°C                                                      | _      | _    | 1    | mA   |  |

|                  | current                      | VCE = VCES                     | Tj = 125°C                                                     | _      | _    | 10   | IIIA |  |

#### **CONTROL (PROTECTION) PART**

| Cumbal   | Parameter                    |                                                     | Condition |                            |         | Limits |      |      |

|----------|------------------------------|-----------------------------------------------------|-----------|----------------------------|---------|--------|------|------|

| Symbol   | Parameter                    |                                                     | Condition |                            | Min.    | Тур.   | Max. | Unit |

|          |                              | VD = VDB = 15V Total of                             |           | of VP1-VPC, VN1-VNC        | _       | _      | 5.00 | mA   |

| lD       | Circuit current              | VIN = 5V                                            | Vufb-     | VUFS, VVFB-VVFS, VWFB-VWFS | _       | _      | 0.40 | mA   |

| ם ו      | Circuit current              | VD = VDB = 15V                                      | Total o   | of VP1-VPC, VN1-VNC        | _       | _      | 7.00 | mA   |

|          |                              | VIN = 0V                                            | VUFB-\    | VUFS, VVFB-VVFS, VWFB-VWFS | _       | _      | 0.55 | mA   |

| VFOH     | Fault output voltage         | Vsc = 0V, Fo circuit pull-up to 5V with $10k\Omega$ |           |                            | 4.9     | _      | _    | V    |

| VFOL     | Tault output voltage         | VSC = 1V, IFO = 1mA                                 |           |                            | _       | _      | 0.95 | V    |

| VSC(ref) | Short circuit trip level     | $T_j = 25^{\circ}C, VD = 15V$ (Note 4)              |           | 0.43                       | 0.48    | 0.53   | V    |      |

| lin      | Input current                | VIN = 5V                                            | VIN = 5V  |                            | 1.0     | 1.5    | 2.0  | mA   |

| UVDBt    |                              |                                                     |           | Trip level                 | 10.0    | _      | 12.0 | V    |

| UVDBr    | Supply circuit under-voltage | T <sub>i</sub> ≤ 125°C                              |           | Reset level                | 10.5    | _      | 12.5 | V    |

| UVDt     | protection                   | 1j≤125 C                                            |           | Trip level                 | 10.3    | _      | 12.5 | V    |

| UVDr     |                              |                                                     |           | Reset level                | 10.8    | _      | 13.0 | V    |

| tFO      | Fault output pulse width     | CFO = 22nF (Note 5)                                 |           | 1.0                        | 1.8     | _      | ms   |      |

| Vth(on)  | ON threshold voltage         | Applied between LID V/D W/D V/DO LINE V/N W/N V/NO  |           | 2.1                        | 2.3     | 2.6    | V    |      |

| Vth(off) | OFF threshold voltage        | Applied between UP, VP, WP-VPC, UN, VN, WN-VNC      |           |                            | 0.8 1.4 | 2.1    | V    |      |

Note 4: Short circuit protection is functioning only at the low-arms. Please select the value of the external shunt resistor such that the SC trip-

level is less than 85 A.

5: Fault signal is output when the low-arms short circuit or control supply under-voltage protective functions operate. The fault output pulsewidth tFo depends on the capacitance value of CFo according to the following approximate equation: CFo = 12.2 X 10<sup>-6</sup> X tFo [F].

# TRANSFER-MOLD TYPE **INSULATED TYPE**

#### **MECHANICAL CHARACTERISTICS AND RATINGS**

| Developmentary     | Condition           |                      | Limits |      |      | l locia |

|--------------------|---------------------|----------------------|--------|------|------|---------|

| Parameter          |                     | Min.                 | Тур.   | Max. | Unit |         |

| Mounting torque    | Mounting screw : M4 | Recommended 1.18 N·m | 0.98   | _    | 1.47 | N⋅m     |

| Weight             |                     |                      | _      | 65   | _    | g       |

| Heat-sink flatness |                     | (Note 6)             | -50    | _    | 100  | μm      |

#### Note 6: Measurement point of heat-sink flatness

#### **RECOMMENDED OPERATION CONDITIONS**

| 0                           | Downstein One Hitter            |                                                          | Limits |      |      | I I alt |

|-----------------------------|---------------------------------|----------------------------------------------------------|--------|------|------|---------|

| Symbol                      | Parameter                       | Condition                                                | Min.   | Тур. | Max. | Unit    |

| Vcc                         | Supply voltage                  | Applied between P-N                                      | 0      | 300  | 400  | V       |

| VD                          | Control supply voltage          | Applied between VP1-VPC, VN1-VNC                         | 13.5   | 15.0 | 16.5 | V       |

| VDB                         | Control supply voltage          | Applied between VUFB-VUFS, VVFB-VVFS, VWFB-VWFS          | 13.0   | 15.0 | 18.5 | V       |

| $\Delta V$ D, $\Delta V$ DB | Control supply variation        |                                                          |        | _    | 1    | V/μs    |

| tdead                       | Arm shoot-through blocking time | For each input signal, Tf ≤ 100°C                        |        | _    | _    | μs      |

| fPWM                        | PWM input frequency             | $T_f \le 100^{\circ}C$ , $T_j \le 125^{\circ}C$          |        | 5    | _    | kHz     |

|                             |                                 | Vcc = 300V, VD = 15V, fc = 5kHz                          |        |      |      |         |

| lo                          | Allowable r.m.s. current        | P.F = 0.8, sinusoidal                                    | _      | _    | 23   | Arms    |

|                             |                                 | $T_j \le 125^{\circ}C$ , $T_f \le 100^{\circ}C$ (Note 7) |        |      |      |         |

| PWIN                        | Minimum input pulse width       | ON (Note 8)                                              | 300    | _    | _    | ns      |

| VNC                         | VNC variation                   | between VNC-N (including surge)                          | -5.0   | _    | 5.0  | V       |

Note 7: The allowable r.m.s. current value depends on the actual application conditions.

8: The input pulse width less than PWIN might make no response.

TRANSFER-MOLD TYPE INSULATED TYPE

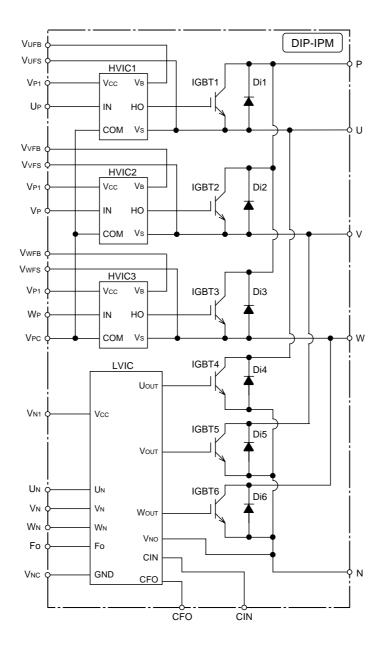

Fig. 4 THE DIP-IPM INTERNAL CIRCUIT

# TRANSFER-MOLD TYPE INSULATED TYPE

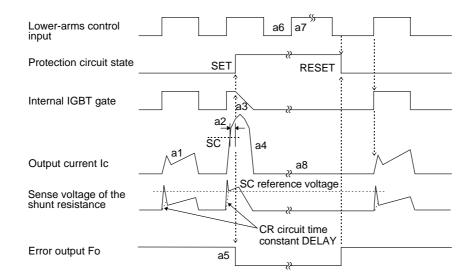

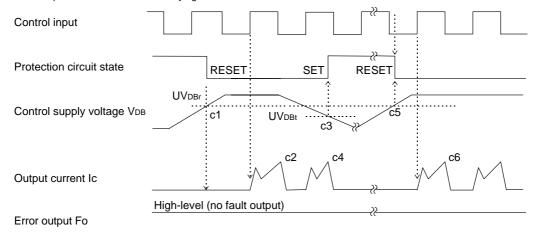

## Fig. 5 TIMING CHARTS OF THE DIP-IPM PROTECTIVE FUNCTIONS

# [A] Short-Circuit Protection (Lower-arms only)

(With the external shunt resistance and CR connection)

- a1. Normal operation: IGBT ON and carrying current.

- a2. Short circuit current detection (SC trigger).

- a3. Hard IGBT gate interrupt.

- a4. IGBT turns OFF.

- a5. Fo timer operation starts: The pulse width of the Fo signal is set by the external capacitor CFo.

- a6. Input "L": IGBT OFF state.

- a7. Input "H": IGBT ON state, but during the Fo active signal period the IGBT doesn't turn ON.

- a8. IGBT OFF state.

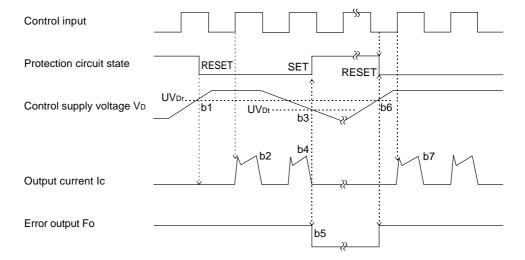

#### [B] Under-Voltage Protection (Lower-arm, UVD)

- b1. Control supply voltage rises: After the voltage level reaches UVDr, the circuits start to operate when next input is applied.

- b2. Normal operation: IGBT ON and carrying current.

- b3. Under voltage trip (UVDt).

- b4. IGBT OFF in spite of control input condition.

- b5. Fo operation starts.

- b6. Under voltage reset (UVDr).

- b7. Normal operation: IGBT ON and carrying current.

## TRANSFER-MOLD TYPE **INSULATED TYPE**

#### [C] Under-Voltage Protection (Upper-arm, UVDB)

- c1. Control supply voltage rises: After the voltage reaches UVDBr, the circuits start to operate when next input is applied. c2. Normal operation: IGBT ON and carrying current.

- c3. Under voltage trip (UVDBt).

- c4. IGBT OFF in spite of control input condition, but there is no Fo signal output.

- c5. Under voltage reset (UVDBr).

- c6. Normal operation: IGBT ON and carrying current.

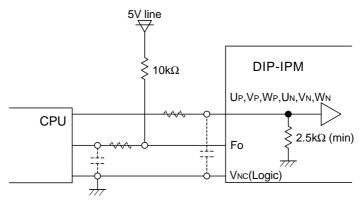

Fig. 6 RECOMMENDED CPU I/O INTERFACE CIRCUIT

Note: RC coupling at each input (parts shown dotted) may change depending on the PWM control scheme used in the application and the wiring impedance of the application's printed circuit board. The DIP-IPM input signal section integrates a  $2.5k\Omega(min)$  pull-down resistor. Therefore, when using a external filtering resistor, care must be taken to satisfy the turn-on threshold voltage requirement.

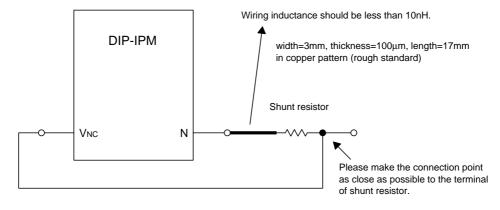

Fig. 7 RECOMMENDED WIRING OF SHUNT RESISTANCE

TRANSFER-MOLD TYPE INSULATED TYPE

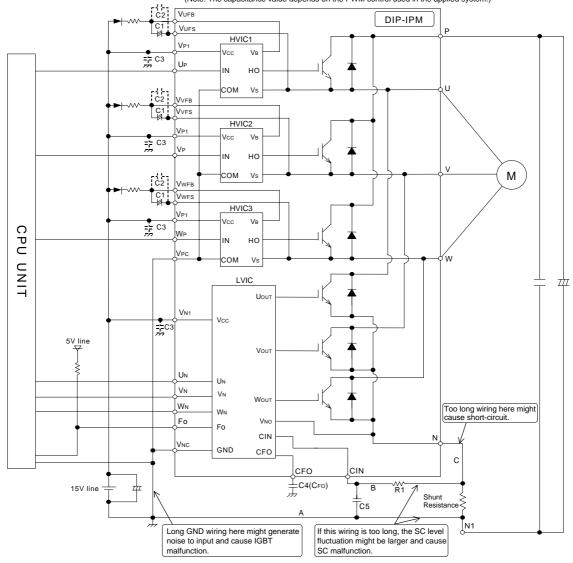

### Fig. 8 TYPICAL DIP-IPM APPLICATION CIRCUIT EXAMPLE

C1:Tight tolerance temp-compensated electrolytic type C2,C3: 0.22~2µF R-category ceramic capacitor for noise filtering. (Note: The capacitance value depends on the PWM control used in the applied system.)

- Note 1: To prevent the input signals oscillation, the wiring of each input should be as short as possible. (2cm~3cm or less)

- 2: By virtue of integrating an application specific type HVIC inside the module, direct coupling to CPU terminals without any opto-coupler or transformer isolation is possible.

- 3: Fo output is open collector type. This signal line should be pulled up to the positive side of the 5V power supply with approximately 10kΩ resistor.

- 4: Fo output pulse width is determined by the external capacitor between CFO and Vnc terminals (CFO). (Example : CFO = 22 nF → tFO = 1.8 ms (typ.))

- 5: The logic of input signal is high-active. The DIP-IPM input signal section integrates a 2.5kΩ (min) pull-down resistor. Therefore, when using external filtering resistor, care must be taken to satisfy the turn-on threshold voltage requirement.

- **6:** To prevent malfunction of protection, The wiring of A, B, C should be as short as possible.

- 7: Please set the R<sub>1</sub>C<sub>5</sub> time constant in the range  $1.5\sim2\mu s$ .

- 8: Each capacitor should be located as nearby the pins of the DIP-IPM as possible.

- 9: To prevent surge destruction, the wiring between the smoothing capacitor and the P&N1 pins should be as short as possible. Approximately a 0.1~0.22μF snubber capacitor between the P&N1 pins is recommended.