**BUS ARBITER**

#### **DESCRIPTION**

The M5L8289P is a system bus ("MULTIBUS) arbiter for the MELPS 86, 88 16-bit microprocessors. When a request for access to the system bus is made by any of these microprocessors, the M5L8289P prevents simultaneous access by two or more processors by allowing only the first processor which requests access to access the system, preventing all others from accessing the system bus. It generates the required signals for bus access. ("MULTIBUS is a registered trademark of Intel Corporation.)

#### **FEATURES**

- MULTIBUS compatible

- Usable in multiprocessing systems using the MELPS 86, 88 microprocessors

- Four modes of request and bus surrender are possible

- Low power dissipation

#### **APPLICATION**

Bus arbitration for MULTIBUS boards using the MELPS 86, 88 or 8089

#### **FUNCTION**

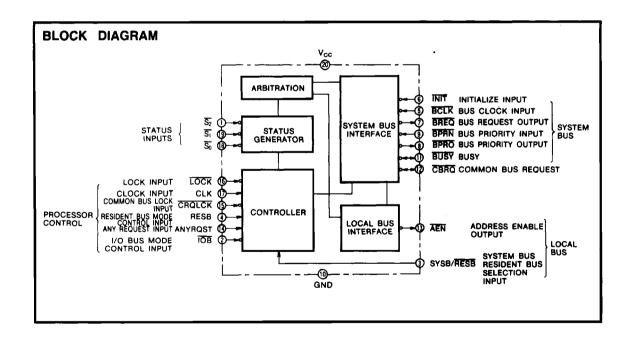

The M5L8289P is a bus arbiter for <sup>R</sup>MULTIBUS boards using the MELPS 86, 88 microprocessors. When several processors are connected to the system bus (<sup>R</sup>MULTIBUS), it is necessary to prevent two or more processors from attempting to access the system bus simultaneously.

This function is performed by the M5L8289P, which decodes the processor status, and if access to the system bus

is required, prevents other processors from attempting system bus access by generating the required control signals.

**BUS ARBITER**

#### **FUNCTIONAL DESCRIPTION**

The M5L8289P decodes the status signals  $\overline{S}_0 \sim \overline{S}_2$  from the processor, and requests system bus privileges or surrenders them. The conditions for such operation are shown in Table 1. As shown in the Table 1, the following four modes are possible for use with boards of various types.

#### (1) Single Bus Mode

In this mode there is neither memory nor I/O ports on the board, and the processor accesses only the system bus.

#### (2) I/O Bus Mode

In this mode I/O ports exist on the board, and the processor accesses only these. For this mode the M5L8289P outputs a system bus request signal only for memory access.

#### (3) Resident Bus Mode

In this mode both memory and/or I/O port(s) exist on the board and the processor can access both on the system bus. In this mode the chip select signal (active low) for I/O ports and memory on the system bus is input to SYSB/RESB. By doing this, when the I/O port(s) and memory on the board are accessed, the M5L8289P does not output a request signal to the system bus.

#### (4) I/O Bus Mode Resident Bus Mode

In this mode both I/O ports and memory are existent on the board, and only the I/O port on the board is accessed.

In this mode the chip select signal (active low) for memory on the board is input to SYSB/RESB. By doing this, the M5L8289P outputs a request signal to the system bus when system memory is accessed.

In addition, the M5L8289P has the following control inputs.

#### LOCK

This signal locks the bus arbitrate function when it is low, the M5L8289P continues to output a request signal to the system bus, and once acquired, setting  $\overline{LOCK}$  to a high level retains bus privileges until the conditions listed in Table 1 are satisfied. Normally, this input is connected to th  $\overline{LOCK}$  output of the processor.

### • CRQLCK

This signal locks the arbitrate function by CBRQ. When set to low, the bus privilege surrender conditions listed in Table 1 in which CBRQ are input, are ignored. This input is set to low level when it is desired to prevent low-priority arbiters from acquiring bus privileges.

#### ANYROST

Even after one bus access has been completed, the M5L8289P does not surrender bus privileges until the surrender conditions listed in Table 1 are satisfied. However, by setting the ANYRQST input to high, the bus can be freed after each single access, thereby facilitating the acquisition of bus privileges by low-priority arbiters.

#### **BUS ARBITER**

Table 1 M5M8289P Modes and Bus Request and surrender Conditions

| Status                |                  |    | I/O Bus  Resident bus mode only |   | is mode only | I/O Bus mode re | Single bus mode |                 |   |

|-----------------------|------------------|----|---------------------------------|---|--------------|-----------------|-----------------|-----------------|---|

|                       |                  |    | IOB=L<br>RESB=L                 |   | :=н<br>в=н   |                 | }=∟<br>B=H      | IOB=H<br>RESB=L |   |

| Command               | $\overline{S}_2$ | Sı | S <sub>1</sub> S <sub>0</sub>   |   | SYSB/RESB=H  | SYSB/RESB=H     | SYSB/RESB=H     | SYSB/RESB=L     |   |

| Interrupt acknowledge | 0                | 0  | 0                               | × | 0            | ×               | ×               | ×               | 0 |

| I/O Port read         | 0                | 0  | 1                               | × | 0            | ×               | ×               | ×               | 0 |

| I/O Write             | 0                | 1  | 0                               | × | 0            | ×               | ×               | ×               | 0 |

| Halt                  | 0                | 1  | 1                               | × | ×            | ×               | ×               | ×               | × |

| Instruction fetch     | 1                | 0  | 0                               | 0 | 0            | ×               | 0               | ×               | 0 |

| Memory read           | 1                | 0  | 1                               | 0 | 0            | ×               | 0               | ×               | 0 |

| Memory write          | 1                | 1  | 0                               | 0 | 0            | ×               | 0               | ×               | 0 |

| Passive cycle         | 1                | 1  | 1                               | × | ×            | ×               | ×               | ×               | × |

O ····· A request signal is output by the system bus.

X ···· The system bus privileges are surrendered.

| Mada              | in       | put | Bus request condition                   | Bus surrender condition (Note 1)  |  |  |

|-------------------|----------|-----|-----------------------------------------|-----------------------------------|--|--|

| Mode              | IOB RESB |     | (excluding halt and passive cycles)     | pas salvenides condition (More 1) |  |  |

| Single bus mode   | Н        | L   | All bus access states                   | HLT+(TI-CBRQ)+HPBRQ               |  |  |

| Resident bus      | T        | 1   | (0V00 = 000 + 1-4) (D                   | ((SYSB/RESB=L+TI)·CBRQ)           |  |  |

| mode only         | Н        |     | (SYSB/RESB=high) (Bus access state)     | +HLT+HPBRQ                        |  |  |

|                   |          |     |                                         | (I/O Access state+T1)-CBRQ)+HLT   |  |  |

| I/O Bus mode only | L        | L   | All memory access states                | +HPERQ                            |  |  |

| /O Bus mode       |          | (2) | ((I/O Access state +(SYSB/RESB=low))    |                                   |  |  |

| resident bus mode | L        | H   | (SYSB/RESB=high)-(Memory access states) | CBRQ + HPBRQ HLT +HPBRQ           |  |  |

Note 1: When LOCK=low, the bus is not released under any circumstances.

When CRQLCK=low, the bus is not released even when low-priority arbiters request it.

2 : HLT·······Halt state

TI······Idle (passive) state

CBRQ·······CBRQ=low

HPBRQ ·····Indicates that a high-priority arbiter is requesting the bus (BPRN=high)

## **BUS ARBITER**

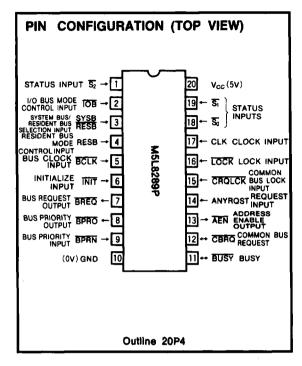

## PIN DESCRIPTION

| Pin                                                    | Name                                    | Input or output | Function                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------|-----------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\overline{S_0}$ , $\overline{S_1}$ , $\overline{S_2}$ | Status input                            | ln              | Status input from the processor. The M5L8289P decodes this signal and based on it, requests or surrenders bus privileges.                                                                                                                                                                                                                                                |

| CLK                                                    | Clock input                             | In              | This is the same clock input as used on the processor, and used for decoding of the status. It receives the clock from the M5L8284AP.                                                                                                                                                                                                                                    |

| LOCK                                                   | Lock input                              | In              | This is the lock input signal from the processor. When LOCK=low, the M5L8289P will, in no circumstances, surrender bus privileges.                                                                                                                                                                                                                                       |

| CROLCK                                                 | Common bus request lock input           | In              | This is the lock signal for arbitration from a common bus request. When CRQLCK = low, the M5L8289P ignores bus surrendering conditions by signal CBRQ.                                                                                                                                                                                                                   |

| RESB                                                   | Resident bus<br>mode control<br>input   | In              | This is the M5L8289P mode setting input. When RESB=high, the M5L8289P is in the resident bus mode.                                                                                                                                                                                                                                                                       |

| ЮВ                                                     | I/O Bus mode control input              | In              | This is an M5L8289P mode settling input. When IOB=low, the M5L8289P is in the I/O bus mode.                                                                                                                                                                                                                                                                              |

| ANYRQST                                                | Any request input                       | in              | This controls the bus surrendering conditions for the M5L8289P. When ANYRQST = low, the M5L8289P re-<br>leases the bus under the conditions listed in Table 1. When ANYRQST = high, as soon as CBRQ goes low,<br>the bus is released. Therefore, by setting ANYRQST to high and CBRQ to low, the M5L8289P can be made<br>to release the bus after a single access.       |

| SYSB/<br>RESB                                          | System bus/resident bus selection input | In              | This input is valid when the M5L8289P is in the resident bus mode. When SYSB/RESB=low, this means that the processor is accessing the bus on the board, and the M5L8289P does not output a request to the system bus. When SYSB/RESB=high, this indicates that the processor is accessing the system bus, and the M5L8289P outputs the request signal to the system bus. |

| BCLK                                                   | Bus lock<br>input                       | In              | This is the clock for arbitration of other boards. The M5L8289P performs arbitration in synchronous with this clock. It is fed from the system bus BCLK signal.                                                                                                                                                                                                          |

| INIT                                                   | Initialize<br>input                     | In              | This line resets the arbitration circuit. Immediately after resetting, none of the arbiters have system bus privileges. This input is fed from the system bus INIT signal.                                                                                                                                                                                               |

| BREQ                                                   | Bus request output                      | Out             | This signal requests system bus privileges. It is used as the system bus BREQ signal.                                                                                                                                                                                                                                                                                    |

| BPRN                                                   | Bus priority input                      | ln              | This signal indicates whether a high-priority arbiter has requested privileges or not. When BPRN=low, a high-priority arbiter has not requested privileges and when BPRN=high, this indicates that a high-priority arbiter has requested privileges. This input is fed from the system bus BPRN signal.                                                                  |

| BPRO                                                   | Bus priority output                     | Out             | This signal indicates whether the M5L8289P or high-order arbiter has requested the bus. When BPRO low, there was a bus request and when BPRO=high, there was no bus request. This signal is used as the system bus BPRO signal.                                                                                                                                          |

| BUSY                                                   | Busy                                    | In/Out          | This signal indicates that the system bus has been acquired. When BUSY=low, the bus is busy and when BUSY=high, it indicates that no arbiter has acquired the bus privileges. When the M5L8289P has acquired bus privileges, a low-level output (open collector) is made. This signal is used as the system bus BUSY signal.                                             |

| CBRQ                                                   | Common bus request                      | In/Out          | This signal indicates when any arbiter has requested the system bus. When CBRQ=low, the M5L8289P releases the bus according to the conditions listed in Table1. When making a request of the system bus CBRQ is output as low (open collector). This signal is used as the system bus CBRQ signal.                                                                       |

| AEN                                                    | Address<br>enable input                 | Out             | This signal informs the bus buffer on the board that the system bus has been acquired. It is connected to the address and data buffer outputs, and the output enable line on the board as well as the M5L8288P AEN line.                                                                                                                                                 |

## **BUS ARBITER FOR**

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol         | Parameter             | Conditions | Ratings        | Unit |

|----------------|-----------------------|------------|----------------|------|

| Vcc            | Supply voltage        |            | -0.5~7         | V    |

| V <sub>1</sub> | Input voltage         |            | -1~5.5         | V    |

| V <sub>o</sub> | Output voltage        |            | -0.5~7         | V    |

| Topr           | Operating temperature |            | 0~75           | Č    |

| Tstg           | Storage temperature   |            | <b>−65~150</b> | r    |

## RECOMMENDED OPERATING CONDITIONS ( $\tau_a=0\sim75^{\circ}$ C, unless otherwise noted)

| 0                |                   |               |                          | Unit           |     |      |    |

|------------------|-------------------|---------------|--------------------------|----------------|-----|------|----|

| Symbol           |                   | Parameter     | Min                      | Nom            | Max | Unit |    |

| Vcc              | Supply voltage    |               |                          | 4. 5           | 5   | 5. 5 | ٧  |

| Іон              | High-level output | BUSY, CBRQ,   | V <sub>OH</sub> ≩ 2. 4V  | Open collector |     |      |    |

|                  | current           | Other output, | V <sub>OH</sub> ≥2. 4V   | 0              |     | 400  | μΑ |

| Low-level output | Ť                 | BUSY, CBRQ,   | V <sub>OL</sub> ≤ 0. 45V | 0              | · · | 20   |    |

|                  | ,                 | AEN           | V <sub>OL</sub> ≤0. 45V  | 0              |     | 16   | mA |

|                  | current           | BPRO, BREQ.   | V <sub>OL</sub> ≤0. 45V  | 0              |     | 10   |    |

## **ELECTRICAL CHARACTERISTICS** ( $T_a=0\sim75$ °C , $V_{cc}=5V\pm10\%$ , unless otherwise noted)

|                 | Parameter.               |                     | Task and distance                             |                | Limits |       |      |  |

|-----------------|--------------------------|---------------------|-----------------------------------------------|----------------|--------|-------|------|--|

| Symbol          |                          | Parameter           | Test conditions                               | Min            | Тур    | Мах   | Unit |  |

| VIL             | Low-level input voltage  |                     |                                               |                |        | 0.8   | ٧    |  |

| ViH             | High-level input voltage |                     |                                               | 2. 0           |        |       | ٧    |  |

|                 |                          | BUSY, CBRQ IoL=20mA | I <sub>OL</sub> =20mA                         |                |        | 0. 45 |      |  |

| Vol             | Low-level                | AEN                 | I <sub>OL</sub> =16mA                         |                |        | 0. 45 | V    |  |

|                 | output voltage           | BPRO, BREQ          | I <sub>OL</sub> =10mA                         |                |        | 0, 45 |      |  |

|                 | High-level               | BUSY, CBRQ          |                                               | Open collector |        | v     |      |  |

| V <sub>OH</sub> | output voltage           | AEN, BPRO, BREQ     | I <sub>OH</sub> =400μA                        | 2. 4           |        |       | v    |  |

| V <sub>IC</sub> | Input clamp volta        | ge                  | V <sub>CC</sub> =4.50V, I <sub>C</sub> =-5mA  |                |        | -1    | V    |  |

| I <sub>IL</sub> | Low-level input c        | urrent              | V <sub>CC</sub> =5.50V, V <sub>F</sub> =0.45V |                | ,      | -0.5  | mA   |  |

| I <sub>IH</sub> | High-level input current |                     | Vcc=5.50V, Vn=5.50V                           |                | _      | 60    | μA   |  |

| Icc             | Supply current           |                     |                                               |                |        | 120   | mA   |  |

| CiN             | 1,                       | Status              | -1,000                                        |                |        | 25    |      |  |

|                 | Input capcitance         | Others              | f=1MHz, V <sub>B2AS</sub> =2.5V               |                |        | 12    | ρF   |  |

**BUS ARBITER**

## TIMING REQUIREMENT (Ta=0~75°C , Vcc=5V±10% , unless otherwise noted)

| Symbol                                    | Parameter                     | Alternate          | Test conditions |                    | Unit                |                      |      |

|-------------------------------------------|-------------------------------|--------------------|-----------------|--------------------|---------------------|----------------------|------|

| Symbol                                    | Parameter                     | symbol             | rest conditions | Min                | Тур                 | Max                  | Unit |

| tc(clk)                                   | CLK cycle period              | t <sub>CLCL</sub>  |                 | 125                |                     |                      | ns   |

| tw(CLKL)                                  | CLK"L" pulse width            | talah              |                 | 65                 |                     |                      | ns   |

| tw(CLKH)                                  | CLK"H" pulse width            | tchcL              |                 | 35                 |                     |                      | ns   |

| t <sub>8u(\$0</sub> ~\$2)                 | Status active setup time      | tsvcн              |                 | 65                 |                     | toucu.10             | ns   |

| th(50~52)                                 | Status active hold time       | t <sub>CHSV</sub>  |                 | 10                 |                     | t <sub>CLCL</sub> 10 | ns   |

| t <sub>8U</sub> ( <u>sō</u> ~ <u>sz</u> ) | Status inactive setup time    | tsHCL              |                 | 50                 |                     |                      | ns   |

| th(डō~ड2)                                 | Status inactive hold time     | tolsh              |                 | 10                 |                     |                      | ns   |

| th(LOCK)                                  | LOCK inactive hold time       | t <sub>CLLL1</sub> |                 | 10                 |                     |                      | ns   |

| tsu(LOCK)                                 | LOCK active setup time        | tolliz             |                 | 40                 |                     |                      | ns   |

| tsu(syse/RESE)                            | SYSB/RESB setup time          | t <sub>CLSR1</sub> |                 | 0                  |                     |                      | ns   |

| th(syse/RESE)                             | SYSB/RESB hold time           | t <sub>CLSR2</sub> |                 | 20                 |                     |                      | ns   |

| tc(BCLK)                                  | BCLK cycle time               | tecec              |                 | 100                |                     |                      | ns   |

| tw(BCLKH)                                 | BCLK"H" pulse width           | t <sub>BHBL</sub>  |                 | 30                 |                     |                      | ns   |

| tsu(BPRU)                                 | BPRN † 1 to BCLK setup time   | tenser             |                 | 15                 |                     |                      | ns   |

| t <sub>su(BUSY)</sub>                     | BUSY 1 1 to BCLK 1 setup time | teyseL             |                 | 20                 |                     |                      | ns   |

| tsu(CBRQ)                                 | CBRQ↑↓to BCLK↓ setup time     | t <sub>CBSBL</sub> |                 | 20                 |                     |                      | ns   |

| t <sub>W(INIT)</sub>                      | INIT pulse width              | t <sub>iViн</sub>  |                 | 3t <sub>BLBL</sub> | +3t <sub>CLCL</sub> |                      | ns   |

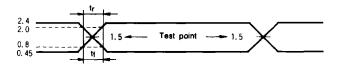

| tr                                        | Input rise time               | ticie              | 0.8~2V          |                    |                     | 20                   | ns   |

| tf                                        | Input fall time               | tiers              | 2~0.8V          |                    |                     | 12                   | ns   |

#### BUS ARBITER

## SWITCHING CHARACTERISTICS ( $\tau_{a}$ =0~75°C , $v_{cc}$ ±5v±5% , unless otherwise noted)

|                         |                                         | Alternate           |                 |     | Limits |     | 11-14 |

|-------------------------|-----------------------------------------|---------------------|-----------------|-----|--------|-----|-------|

| Symbol                  | Parameter                               | symbol              | Test conditions | Min | Тур    | Max | Unit  |

| t <sub>PHL</sub> (BREQ) | BCLK→BREQ 1 , ↓ Delay time              | t <sub>BLBRL</sub>  |                 |     |        | 35  | ns    |

| t <sub>PLH</sub> (BPRO) | BCLK→BPRO↑, ↓ Delay time (See note 2)   | <sup>†</sup> в∟РОН  |                 |     |        | 40  | ns    |

| t <sub>PHL</sub> (BPRÖ) | BPRN↑, ↓→BPRO↑↓ Delay time (See note 2) | t <sub>PNPO</sub>   |                 |     |        | 25  | ns    |

| t <sub>PHL</sub> (BUSY) | BCLK→BUSY I Delay time                  | t <sub>BLBYL</sub>  | 1               |     |        | 60  | ns    |

| t <sub>PLZ</sub> (BUSY) | BCLK→BUSY Float time (See note 3)       | tare/H              |                 |     |        | 35  | ns    |

| t <sub>PLH</sub> (AEN)  | CLK→AEN, ↑ Delay time                   | t <sub>CLAEH</sub>  | 7               |     |        | 65  | ns    |

| t <sub>PHL</sub> (AEN)  | BCLK→AEN, ↓ Delay time                  | TBLAEL              | 7               |     |        | 40  | ns    |

| t <sub>PHL</sub> (CBRQ) | BCLK→CBRQ, ↓ Delay time                 | telcal              |                 |     |        | 60  | ns    |

| t <sub>PLZ</sub> (CBAQ) | BCLK→CBRQ Delay time (See note 3)       | t <sub>B</sub> LCBH |                 |     |        | 35  | ns    |

| tr                      | Output rise time                        | tолон               | 0.8V~2.0V       |     |        | 20  | ns    |

| tf                      | Output fall time (See note 4, 5)        | tohol               | 2. 0V~0. 8V     |     |        | 12  | ns    |

Note 1: Symbol 1, I means rise signal and fall signal.

2: BCLK generate the first BPRO and then BPRO changes lower in the chain are generated through BPRN.

3: Measured at 0.5V above GND

Note 4 : A.C. test wave form.

Note 5 : Load circuit

#### **BUS ARBITER**

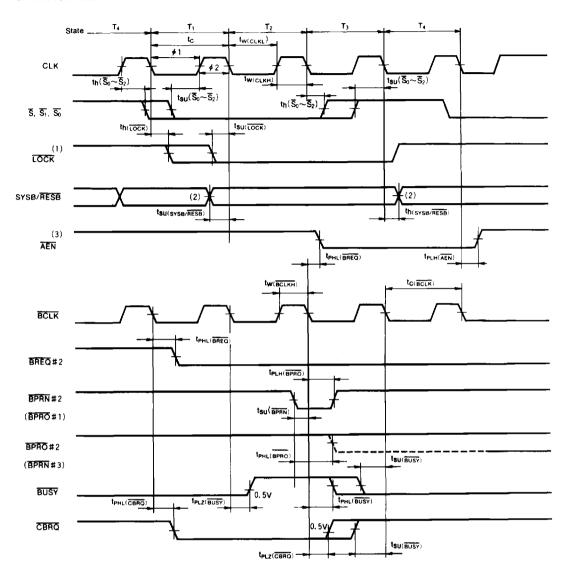

## TIMING DIAGRAM

Note 1: LOCK can be active during any state as long as the relation ships shown above with the respect to CLK are maintained.

LOCK can be inactive asynchronously.

CRQLCK is an asynchronous input signal.

2: Notes is permitted during this time. After ∞2 of T1 and before ∞1 of T4 should be stable.

3: AEN negative-edge is related to CLK, positive-edge to CLK.

ANE positive-edge is generated after as ricrity is lost.