# [ Obsolete product ] Agilent has a new name Keysight Technologies.

Keysight Technologies Inc. is the world's leading electronic measurement company, transforming today's measurement experience through innovations in wireless, modular, and software solutions. With its HP and Agilent legacy, Keysight delivers solutions in wireless communications, aerospace and defense and semiconductor markets with world-class platforms, software and consistent measurement science.

# Agilent HCPL-7710, HCPL-0710 40 ns Propagation Delay, CMOS Optocoupler Data Sheet

## Description

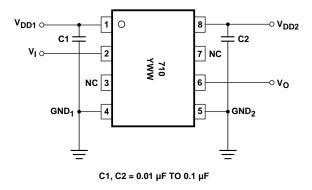

Available in either an 8-pin DIP or SO-8 package style respectively, the HCPL-7710 or HCPL-0710 optocouplers utilize the latest CMOS IC technology to achieve outstanding performance with very low power consumption. The HCPL-x710 require only two bypass capacitors for complete CMOS compatibility.

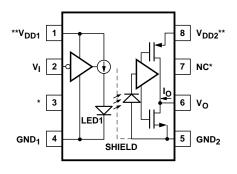

Basic building blocks of the HCPL-x710 are a CMOS LED driver IC, a high speed LED and a CMOS detector IC. A CMOS logic input signal controls the LED driver IC which supplies current to the LED. The detector IC incorporates an integrated photodiode, a high-speed transimpedance amplifier, and a voltage comparator with an output driver.

### **Functional Diagram**

| (POSITIVE LOGIC)                                    |     |   |  |  |  |  |  |  |  |

|-----------------------------------------------------|-----|---|--|--|--|--|--|--|--|

| V <sub>I</sub> , INPUT LED1 V <sub>O</sub> , OUTPUT |     |   |  |  |  |  |  |  |  |

| Н                                                   | OFF | Н |  |  |  |  |  |  |  |

| L                                                   | ON  | L |  |  |  |  |  |  |  |

### **Features**

- +5 V CMOS compatibility

- 8 ns maximum pulse width distortion

- · 20 ns maximum prop. delay skew

- · High speed: 12 Mbd

- · 40 ns maximum prop. delay

- 10 kV/µs minimum common mode rejection

- -40°C to 100°C temperature range

- Safety and regulatory approvals

UL Recognized

3750 V rms for 1 min. per

UL 1577

- CSA Component Acceptance Notice #5

### IEC/EN/DIN EN 60747-5-2

- V<sub>IORM</sub> = 630 Vpeak for HCPL-7710 Option 060

- V<sub>IORM</sub> = 560 Vpeak for HCPL-0710 Option 060

### **Applications**

- Digital fieldbus isolation: DeviceNet, SDS, Profibus

- AC plasma display panel level shifting

- · Multiplexed data transmission

- Computer peripheral interface

- · Microprocessor system interface

- \* Pin 3 is the anode of the internal LED and must be left unconnected for guaranteed data sheet performance. Pin 7 is not connected internally.

- \*\* A 0.1 µF bypass capacitor must be connected between pins 1 and 4, and 5 and 8.

**CAUTION:** It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

### **Selection Guide**

| 8-Pin DIP | Small Outline |

|-----------|---------------|

| (300 Mil) | SO-8          |

| HCPL-7710 | HCPL-0710     |

### **Ordering Information**

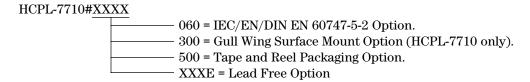

Specify Part Number followed by Option Number (if desired)

### Example

No Option and Option 300 contain 50 units (HCPL-7710), 100 units (HCPL-0710) per tube. Option 500 contain 1000 units (HCPL-7710), 1500 units (HCPL-0710) per reel. Option data sheets available. Contact Agilent sales representative or authorized distributor.

Remarks: The notation "#" is used for existing products, while (new) products launched since 15th July 2001 and lead free option will use "-"

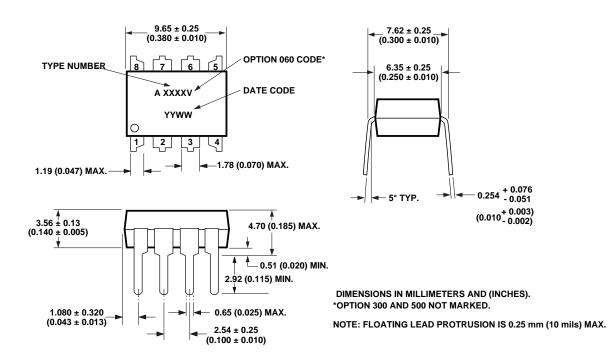

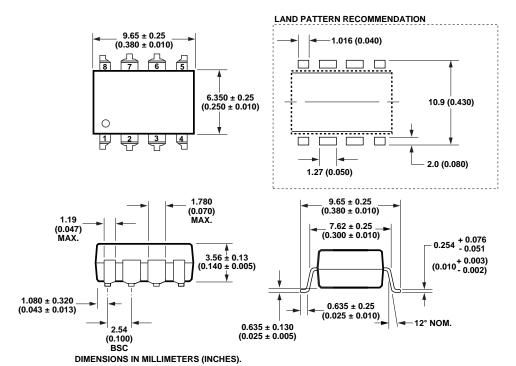

# Package Outline Drawing HCPL-7710 8-Pin DIP Package

### **Package Outline Drawing**

### HCPL-7710 Package with Gull Wing Surface Mount Option 300

LEAD COPLANARITY = 0.10 mm (0.004 INCHES).

NOTE: FLOATING LEAD PROTRUSION IS 0.25 mm (10 mils) MAX.

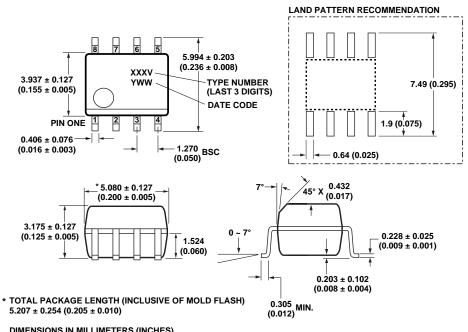

### **Package Outline Drawing**

### HCPL-0710 Outline Drawing (Small Outline SO-8 Package)

DIMENSIONS IN MILLIMETERS (INCHES). LEAD COPLANARITY = 0.10 mm (0.004 INCHES) MAX.

OPTION NUMBER 500 NOT MARKED.

NOTE: FLOATING LEAD PROTRUSION IS 0.15 mm (6 mils) MAX.

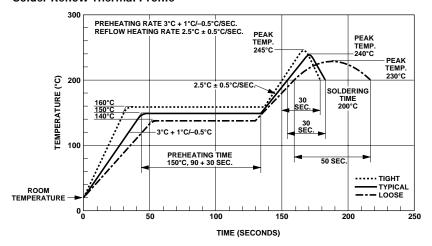

### **Solder Reflow Thermal Profile**

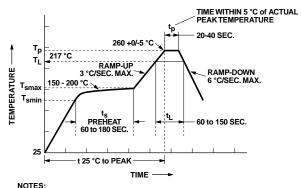

### Recommended Pb-Free IR Profile

THE TIME FROM 25 °C to PEAK TEMPERATURE = 8 MINUTES MAX.  $T_{smax}$  = 200 °C,  $T_{smin}$  = 150 °C

### **Regulatory Information**

The HCPL-x710 have been approved by the following organizations:

### UL

Recognized under UL 1577, component recognition program, File E55361.

### **CSA**

Approved under CSA Component Acceptance Notice #5, File CA 88324.

### IEC/EN/DIN EN 60747-5-2

Approved under: IEC 60747-5-2:1997 + A1:2002 EN 60747-5-2:2001 + A1:2002 DIN EN 60747-5-2 (VDE 0884 Teil 2):2003-01. (Option 060 only)

### **Insulation and Safety Related Specifications**

| Value                                                  |        |      |      |       |                                                                                               |  |  |

|--------------------------------------------------------|--------|------|------|-------|-----------------------------------------------------------------------------------------------|--|--|

| Parameter                                              | Symbol | 7710 | 0710 | Units | Conditions                                                                                    |  |  |

| Minimum External Air<br>Gap (Clearance)                | L(101) | 7.1  | 4.9  | mm    | Measured from input terminals to output terminals, shortest distance through air.             |  |  |

| Minimum External<br>Tracking (Creepage)                | L(102) | 7.4  | 4.8  | mm    | Measured from input terminals to output terminals, shortest distance path along body.         |  |  |

| Minimum Internal Plastic<br>Gap (Internal Clearance)   |        | 0.08 | 0.08 | mm    | Insulation thickness between emitter and detector; also known as distance through insulation. |  |  |

| Tracking Resistance<br>(Comparative Tracking<br>Index) | СТІ    | ≥175 | ≥175 | Volts | DIN IEC 112/VDE 0303 Part 1                                                                   |  |  |

| Isolation Group                                        |        | Illa | IIIa |       | Material Group (DIN VDE 0110, 1/89,<br>Table 1)                                               |  |  |

All Agilent data sheets report the creepage and clearance inherent to the optocoupler component itself. These dimensions are needed as a starting point for the equipment designer when determining the circuit insulation requirements. However, once mounted on a printed circuit

board, minimum creepage and clearance requirements must be met as specified for individual equipment standards. For creepage, the shortest distance path along the surface of a printed circuit board between the solder fillets of the input and output leads must be considered.

There are recommended techniques such as grooves and ribs which may be used on a printed circuit board to achieve desired creepage and clearances. Creepage and clearance distances will also change depending on factors such as pollution degree and insulation level.

| IEC/EN/DIN EN 60747-5-2 Insulation Related Characterist           | ics (Option 060       | )                |                  |        |  |

|-------------------------------------------------------------------|-----------------------|------------------|------------------|--------|--|

|                                                                   |                       | HCPL-7710        | HCPL-0710        |        |  |

| Description                                                       | Symbol                | Option 060       | Option 060       | Units  |  |

| Installation classification per DIN VDE 0110/1.89, Table 1        |                       |                  |                  |        |  |

| for rated mains voltage ≤150 V rms                                |                       | I-IV             | I-IV             |        |  |

| for rated mains voltage ≤300 V rms                                |                       | I-IV             | 1-111            |        |  |

| for rated mains voltage ≤450 V rms                                |                       | 1-111            |                  |        |  |

| Climatic Classification                                           |                       | 55/100/21        | 55/100/21        |        |  |

| Pollution Degree (DIN VDE 0110/1.89)                              |                       | 2                | 2                |        |  |

| Maximum Working Insulation Voltage                                | V <sub>IORM</sub>     | 630              | 560              | V peak |  |

| Input to Output Test Voltage, Method b†                           | V <sub>PR</sub>       | 1181             | 1050             | V peak |  |

| $V_{IORM}$ x 1.875 = $V_{PR}$ , 100% Production                   |                       |                  |                  | -      |  |

| Test with t <sub>m</sub> = 1 sec, Partial Discharge < 5 pC        |                       |                  |                  |        |  |

| Input to Output Test Voltage, Method a†                           | $V_{PR}$              | 945              | 840              | V peak |  |

| $V_{IORM}$ x 1.5 = $V_{PR}$ , Type and Sample Test,               |                       |                  |                  | ·      |  |

| t <sub>m</sub> = 60 sec, Partial Discharge < 5 pC                 |                       |                  |                  |        |  |

| Highest Allowable Overvoltage†                                    | V <sub>IOTM</sub>     | 6000             | 4000             | V peak |  |

| (Transient Overvoltage, t <sub>ini</sub> = 10 sec)                |                       |                  |                  | ·      |  |

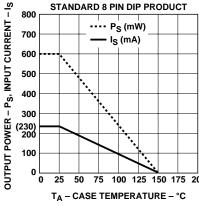

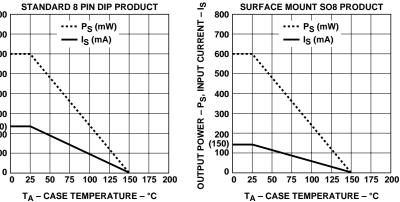

| Safety Limiting Values                                            |                       |                  |                  |        |  |

| (Maximum values allowed in the event of a failure,                |                       |                  |                  |        |  |

| also see Thermal Derating curve, Figure 11.)                      |                       |                  |                  |        |  |

| Case Temperature                                                  | $T_S$                 | 175              | 150              | °C     |  |

| Input Current                                                     | I <sub>S,INPUT</sub>  | 230              | 150              | mA     |  |

| Output Power                                                      | P <sub>S,OUTPUT</sub> | 600              | 600              | mW     |  |

| Insulation Resistance at T <sub>S</sub> , V <sub>10</sub> = 500 V | R <sub>IO</sub>       | ≥10 <sup>9</sup> | ≥10 <sup>9</sup> | Ω      |  |

†Refer to the front of the optocoupler section of the Isolation and Control Component Designer's Catalog, under Product Safety Regulations section IEC/EN/DIN EN 60747-5-2, for a detailed description.

Note: These optocouplers are suitable for "safe electrical isolation" only within the safety limit data. Maintenance of the safety data shall be ensured by means of protective circuits.

Note: The surface mount classification is Class A in accordance with CECC 00802.

| Absolute Maximum Ratings          |                                               |               |                  |             |        |  |  |  |

|-----------------------------------|-----------------------------------------------|---------------|------------------|-------------|--------|--|--|--|

| Parameter                         | Symbol                                        | Min.          | Max.             | Units       | Figure |  |  |  |

| Storage Temperature               | T <sub>S</sub>                                | -55           | 125              | °C          |        |  |  |  |

| Ambient Operating Temperature     | T <sub>A</sub>                                | -40           | +100             | °C          |        |  |  |  |

| Supply Voltages                   | V <sub>DD1</sub> , V <sub>DD2</sub>           | 0             | 6.0              | Volts       |        |  |  |  |

| Input Voltage                     | V <sub>I</sub>                                | -0.5          | $V_{DD1} + 0.5$  | Volts       |        |  |  |  |

| Output Voltage                    | $V_{O}$                                       | -0.5          | $V_{DD2} + 0.5$  | Volts       |        |  |  |  |

| Input Current                     | I <sub>I</sub>                                | -10           | +10              | mA          |        |  |  |  |

| Average Output Current            | I <sub>O</sub>                                |               | 10               | mA          |        |  |  |  |

| Lead Solder Temperature           | 260°C for 10 sec., 1.6 mm below seating plane |               |                  |             |        |  |  |  |

| Solder Reflow Temperature Profile | See                                           | Solder Reflow | Temperature Prof | ile Section |        |  |  |  |

### **Recommended Operating Conditions**

| Parameter                        | Symbol                          | Min. | Max.             | Units | Figure |

|----------------------------------|---------------------------------|------|------------------|-------|--------|

| Ambient Operating Temperature    | T <sub>A</sub>                  | -40  | +100             | °C    |        |

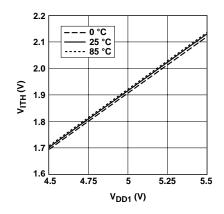

| Supply Voltages                  | $V_{DD1}$ , $V_{DD2}$           | 4.5  | 5.5              | V     |        |

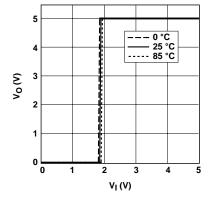

| Logic High Input Voltage         | V <sub>IH</sub>                 | 2.0  | V <sub>DD1</sub> | V     | 1, 2   |

| Logic Low Input Voltage          | V <sub>IL</sub>                 | 0.0  | 0.8              | V     |        |

| Input Signal Rise and Fall Times | t <sub>r</sub> , t <sub>f</sub> |      | 1.0              | ms    |        |

### **Electrical Specifications**

Test conditions that are not specified can be anywhere within the recommended operating range. All typical specifications are at  $T_A = +25$ °C,  $V_{DD1} = V_{DD2} = +5$  V.

| Parameter                                                 | Symbol            | Min. | Тур. | Max. | Units | Test Conditions                                                        | Fig.     | Note |

|-----------------------------------------------------------|-------------------|------|------|------|-------|------------------------------------------------------------------------|----------|------|

| DC Specifications                                         |                   |      |      |      |       |                                                                        |          |      |

| Logic Low Input<br>Supply Current                         | I <sub>DD1L</sub> |      | 6.0  | 10.0 | mA    | V <sub>I</sub> = 0 V                                                   |          | 1    |

| Logic High Input<br>Supply Current                        | I <sub>DD1H</sub> |      | 1.5  | 3.0  | mA    | $V_I = V_{DDI}$                                                        |          |      |

| Input Supply Current                                      | I <sub>DD1</sub>  |      |      | 13.0 | mA    |                                                                        |          |      |

| Output Supply Current                                     | I <sub>DD2</sub>  |      | 5.5  | 11.0 | mA    |                                                                        |          |      |

| Input Current                                             | l <sub>l</sub>    | -10  |      | 10   | μΑ    |                                                                        |          |      |

| Logic High Output                                         | V <sub>OH</sub>   | 4.4  | 5.0  |      | V     | $I_0 = -20  \mu A,  V_1 = V_{IH}$                                      | 1, 2     |      |

| Voltage                                                   |                   | 4.0  | 4.8  |      |       | $I_0 = -4 \text{ mA}, V_1 = V_{1H}$                                    | _        |      |

| Logic Low Output                                          | V <sub>OL</sub>   |      | 0    | 0.1  | V     | $I_0 = 20  \mu A,  V_I = V_{IL}$                                       | _        |      |

| Voltage                                                   |                   |      | 0.5  | 1.0  | •     | $I_0 = 4 \text{ mA}, V_I = V_{IL}$                                     | _        |      |

| Switching Specifications                                  |                   |      |      |      |       |                                                                        |          |      |

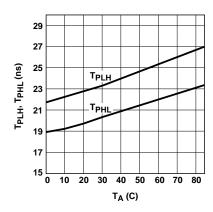

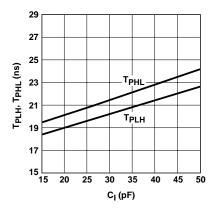

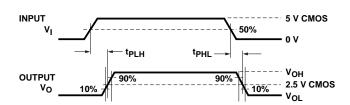

| Propagation Delay Time to Logic Low Output                | t <sub>PHL</sub>  |      | 20   | 40   | ns    | C <sub>L</sub> = 15 pF<br>CMOS Signal Levels                           | 3, 7     | 2    |

| Propagation Delay Time<br>to Logic High Output            | t <sub>PLH</sub>  |      | 23   | 40   | •     |                                                                        |          |      |

| Pulse Width                                               | PW                | 80   |      |      | -     |                                                                        |          | 3    |

| Data Rate                                                 |                   |      |      | 12.5 | MBd   |                                                                        | -        | -    |

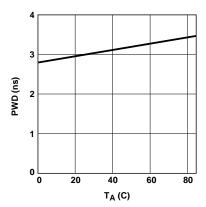

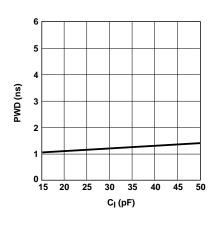

| Pulse Width Distortion                                    | PWD               |      | 3    | 8    | ns    |                                                                        | 4, 8     | 4    |

| t <sub>PHL</sub> - t <sub>PLH</sub>                       |                   |      |      |      | _     |                                                                        |          |      |

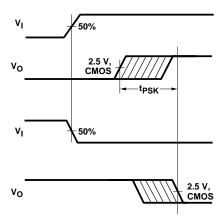

| Propagation Delay Skew                                    | $t_{PSK}$         |      |      | 20   | _     |                                                                        |          | 5    |

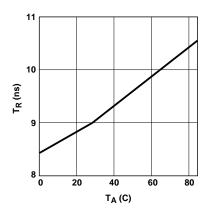

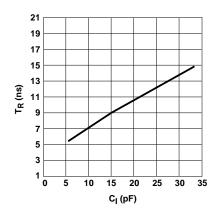

| Output Rise Time<br>(10 - 90%)                            | $t_R$             |      | 9    |      |       |                                                                        | 5, 9     |      |

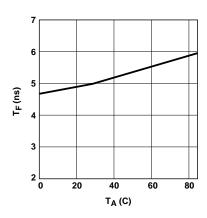

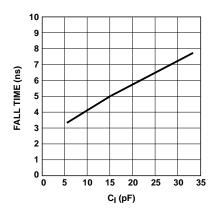

| Output Fall Time<br>(90 - 10%)                            | t <sub>F</sub>    |      | 8    |      |       |                                                                        | 6,<br>10 |      |

| Common Mode<br>Transient Immunity at<br>Logic High Output | CM <sub>H</sub>   | 10   | 20   |      | kV/μs | $V_1 = V_{DD1}, V_0 > 0.8 V_{DD1}, V_{CM} = 1000 V$                    |          | 6    |

| Common Mode<br>Transient Immunity at<br>Logic Low Output  | CM <sub>L</sub>   | 10   | 20   |      |       | $V_1 = 0 \text{ V}, V_0 > 0.8 \text{ V},$<br>$V_{CM} = 1000 \text{ V}$ |          | -    |

| Input Dynamic Power<br>Dissipation<br>Capacitance         | C <sub>PD1</sub>  |      | 60   |      | pF    |                                                                        |          | 7    |

| Output Dynamic Power<br>Dissipation<br>Capacitance        | C <sub>PD2</sub>  |      | 10   |      |       |                                                                        |          | _    |

### **Package Characteristics**

| Parameter                                        |                | Symbol                 | Min.         | Тур.             | Max. | Units | Test Conditions                                          | Fig. | Note        |

|--------------------------------------------------|----------------|------------------------|--------------|------------------|------|-------|----------------------------------------------------------|------|-------------|

| Input-Output Momentary<br>Withstand Voltage      | 0710<br>7710   | V <sub>ISO</sub>       | 3750<br>3750 |                  |      | Vrms  | $RH \le 50\%,$ $t = 1 \text{ min.},$ $T_A = 25^{\circ}C$ |      | 8, 9,<br>10 |

| Resistance<br>(Input-Output)                     |                | R <sub>I-O</sub>       |              | 10 <sup>12</sup> |      | Ω     | $V_{I-O} = 500 \text{ Vdc}$                              |      | 8           |

| Capacitance<br>(Input-Output)                    |                | C <sub>I-O</sub>       |              | 0.6              |      | pF    | f = 1 MHz                                                |      | _           |

| Input Capacitance                                |                | C <sub>I</sub>         |              | 3.0              |      |       |                                                          |      | 11          |

| Input IC Junction-to-Case<br>Thermal Resistance  | -7710<br>-0710 | $\theta_{	extsf{jci}}$ |              | 145<br>160       | _    | °C/W  | Thermocouple located at center                           |      |             |

| Output IC Junction-to-Case<br>Thermal Resistance | -7710<br>-0710 | $\theta_{jco}$         |              | 140<br>135       | -    | _     | underside of package                                     |      |             |

| Package Power Dissipation                        |                | P <sub>PD</sub>        |              |                  | 150  | mW    |                                                          |      |             |

### Notes:

- 1. The LED is ON when V<sub>I</sub> is low and OFF when V<sub>I</sub> is high.

- 2. t<sub>PHL</sub> propagation delay is measured from the 50% level on the falling edge of the V<sub>1</sub> signal to the 50% level of the falling edge of the V<sub>0</sub> signal. t<sub>PLH</sub> propagation delay is measured from the 50% level on the rising edge of the V<sub>1</sub> signal to the 50% level of the rising edge of the V<sub>0</sub> signal.

- 3. Mimimum Pulse Width is the shortest pulse width at which 10% maximum, Pulse Width Distortion can be guaranteed. Maximum Data Rate is the inverse of Minimum Pulse Width. Operating the HCPL-x710 at data rates above 12.5 MBd is possible provided PWD and data dependent jitter increases and relaxed noise margins are tolerable within the application. For instance, if the maximum allowable variation of bit width is 30%, the maximum data rate becomes 37.5 MBd. Please note that HCPL-x710 performances above 12.5 MBd are not guaranteed by Hewlett-Packard.

- PWD is defined as | t<sub>PHL</sub> t<sub>PLH</sub> |.

PWD (percent pulse width distortion) is equal to the PWD divided by pulse width.

- 5. t<sub>PSK</sub> is equal to the magnitude of the worst case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that will be seen between units at any given temperature within the recommended operating conditions.

- 6. CM $_{\rm H}$  is the maximum common mode voltage slew rate that can be sustained while maintaining V $_{\rm O}$  > 0.8 V $_{\rm DD2}$ . CM $_{\rm L}$  is the maximum common mode voltage slew rate that can be sustained while maintaining V $_{\rm O}$  < 0.8 V. The common mode voltage slew rates apply to both rising and falling common mode voltage edges.

- Unloaded dynamic power dissipation is calculated as follows: C<sub>PD</sub> \* V<sub>DD2</sub> \* f + I<sub>DD</sub> \* V<sub>DD</sub>, where f is switching frequency in MHz.

- 8. Device considered a two-terminal device: pins 1, 2, 3, and 4 shorted together and pins 5, 6, 7, and 8 shorted together.

- 9. In accordance with UL1577, each HCPL-0710 is proof tested by applying an insulation test voltage  $\geq$ 4500  $V_{RMS}$  for 1 second (leakage detection current limit,  $I_{I-O} \leq 5 \ \mu A$ ). Each HCPL-7710 is proof tested by applying an insulation test voltage  $\geq$  4500  $V_{RMS}$  rms for 1 second (leakage detection current limit,  $I_{I-O} \leq 5 \ \mu A$ ).

- 10. The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating. For the continuous voltage rating refer to your equipment level safety specification or Agilent Application Note 1074 entitled "Optocoupler Input-Output Endurance Voltage."

- 11. C<sub>1</sub> is the capacitance measured at pin 2 (V<sub>1</sub>).

Figure 1. Typical output voltage vs. input voltage.

Figure 2. Typical input voltage switching threshold vs. input supply voltage.

Figure 3. Typical propagation delays vs. temperature.

Figure 4. Typical pulse width distortion vs. temperature.

Figure 5. Typical rise time vs. temperature.

Figure 6. Typical fall time vs. temperature.

Figure 7. Typical propagation delays vs. output load capacitance.

Figure 8. Typical pulse width distortion vs. output load capacitance.

Figure 9. Typical rise time vs. load capacitance.

SURFACE MOUNT SO8 PRODUCT

Figure 10. Typical fall time vs. load capacitance.

Figure 11. Thermal derating curve, dependence of Safety Limiting Value with case temperature per IEC/EN/DIN EN 60747-5-2.

### **Application Information**

Bypassing and PC Board Layout The HCPL-x710 optocouplers are extremely easy to use. No external interface circuitry is required because the HCPL-x710 use highspeed CMOS IC technology allowing CMOS logic to be connected directly to the inputs and outputs.

As shown in Figure 12, the only external components required for proper operation are two bypass capacitors. Capacitor values should be between 0.01 µF and

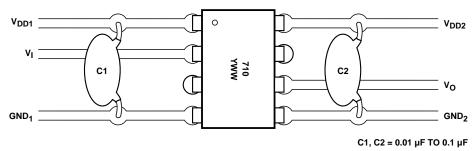

0.1 µF. For each capacitor, the total lead length between both ends of the capacitor and the power-supply pins should not exceed 20 mm. Figure 13 illustrates the recommended printed circuit board layout for the HPCL-x710.

Figure 12. Recommended Printed Circuit Board layout.

Figure 13. Recommended Printed Circuit Board layout.

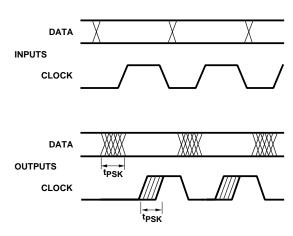

# Propagation Delay, Pulse-Width Distortion and Propagation Delay Skew

Propagation Delay is a figure of merit which describes how quickly a logic signal propagates through a system. The propagation delay from low to high  $(t_{PLH})$  is the amount of time required for an input signal to propagate to the output, causing the output to change from low to high. Similarly, the propagation delay from high to low  $(t_{PHL})$  is the

amount of time required for the input signal to propagate to the output, causing the output to change from high to low. See Figure 14.

Figure 14.

Pulse-width distortion (PWD) is the difference between t<sub>PHL</sub> and t<sub>PLH</sub> and often determines the maximum data rate capability of a transmission system. PWD can be expressed in percent by dividing the PWD (in ns) by the minimum pulse width (in ns) being transmitted. Typically, PWD on the order of 20 - 30% of the minimum pulse width is tolerable. The PWD specification for the HCPL-x710 is 8 ns (10%) maximum across recommended operating conditions. 10% maximum is dictated by the most stringent of the three fieldbus standards, PROFIBUS.

Propagation delay skew,  $t_{PSK}$ , is an important parameter to consider in parallel data applications where synchronization of signals

on parallel data lines is a concern. If the parallel data is being sent through a group of optocouplers, differences in propagation delays will cause the data to arrive at the outputs of the optocouplers at different times. If this difference in propagation delay is large enough it will determine the maximum rate at which parallel data can be sent through the optocouplers.

Propagation delay skew is defined as the difference between the minimum and maximum propagation delays, either  $t_{\rm PLH}$  or  $t_{\rm PHL}$ , for any given group of optocouplers which are operating under the same conditions (i.e., the same drive current, supply voltage, output load, and operating

temperature). As illustrated in Figure 15, if the inputs of a group of optocouplers are switched either ON or OFF at the same time,  $t_{PSK}$  is the difference between the shortest propagation delay, either  $t_{PLH}$  or  $t_{PHL}$ , and the longest propagation delay, either  $t_{PLH}$  or  $t_{PHL}$ .

As mentioned earlier, t<sub>PSK</sub> can determine the maximum parallel data transmission rate. Figure 16 is the timing diagram of a typical parallel data application with both the clock and data lines being sent through the optocouplers. The figure shows data and clock signals at the inputs and outputs of the optocouplers. In this case the data is assumed to be clocked off of the rising edge of the clock.

Figure 15. Propagation delay skew waveform.

Figure 16. Parallel data transmission example.

Propagation delay skew represents the uncertainty of where an edge might be after being sent through an optocoupler. Figure 16 shows that there will be uncertainty in both the data and clock lines. It is important that these two areas of uncertainty not overlap, otherwise the clock signal might arrive before all of the data outputs have settled, or

some of the data outputs may start to change before the clock signal has arrived. From these considerations, the absolute minimum pulse width that can be sent through optocouplers in a parallel application is twice t<sub>PSK</sub>. A cautious design should use a slightly longer pulse width to ensure that any additional

uncertainty in the rest of the circuit does not cause a problem.

The HCPL-x710 optocouplers offer the advantage of guaranteed specifications for propagation delays, pulse-width distortion, and propagation delay skew over the recommended temperature and power supply ranges.

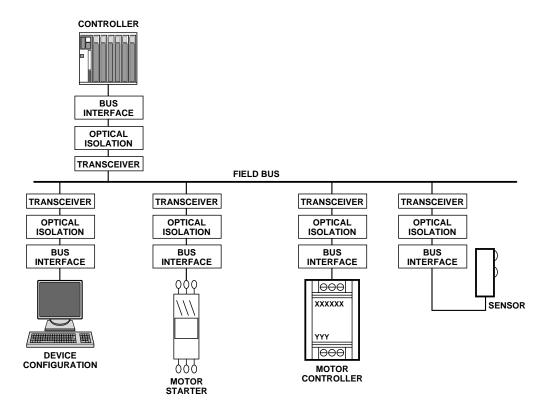

# Digital Field Bus Communication Networks

To date, despite its many drawbacks, the 4 - 20 mA analog current loop has been the most widely accepted standard for implementing process control systems. In today's manufacturing environment, however, automated systems are expected to help manage the process, not merely monitor it. With the advent of digital field bus communication networks such as DeviceNet, PROFIBUS, and Smart Distributed Systems (SDS), gone are the days of constrained information. Controllers can now receive multiple readings from field devices (sensors, actuators, etc.) in addition to diagnostic information.

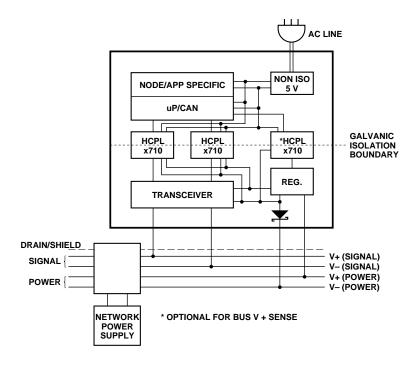

The physical model for each of these digital field bus communication networks is very similar as shown in Figure 17. Each includes one or more buses, an interface unit, optical isolation, transceiver, and sensing and/or actuating devices.

Figure 17. Typical field bus communication physical model.

### Optical Isolation for Field Bus Networks

To recognize the full benefits of these networks, each recommends providing galvanic isolation using Agilent optocouplers. Since network communication is bidirectional (involving receiving data from and transmitting data onto the network), two Agilent optocouplers are needed. By providing galvanic isolation, data integrity is retained via noise reduction and the elimination of false signals. In addition, the

network receives maximum protection from power system faults and ground loops.

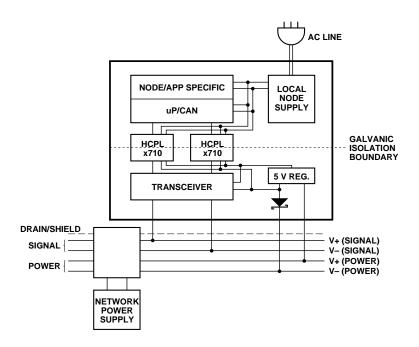

Within an **isolated node**, such as the DeviceNet Node shown in Figure 18, *some* of the node's components are referenced to a ground other than V- of the network. These components could include such things as devices with serial ports, parallel ports, RS232 and RS485 type ports. As shown in Figure 18, power from the network is used only for the

transceiver and input (network) side of the optocouplers.

Isolation of nodes connected to any of the three types of digital field bus networks is best achieved by using the HCPL-x710 optocouplers. For each network, the HCPL-x710 satisify the critical propagation delay and pulse width distortion requirements over the temperature range of 0°C to +85°C, and power supply voltage range of 4.5 V to 5.5 V.

Figure 18. Typical DeviceNet node.

# Implementing DeviceNet and SDS with the HCPL-x710

With transmission rates up to 1 Mbit/s, both DeviceNet and SDS are based upon the same broadcast-oriented, communications protocol — the Controller Area Network (CAN). Three types of isolated nodes are recommended for use on these networks: Isolated Node Powered by the Network (Figure 19),

Isolated Node with Transceiver Powered by the Network (Figure 20), and Isolated Node Providing Power to the Network (Figure 21).

### Isolated Node Powered by the Network

This type of node is very flexible and as can be seen in Figure 19, is regarded as "isolated" because not all of its components have the same ground reference. Yet, all components are still powered by the network. This node contains two regulators: one is isolated and powers the CAN controller, nodespecific application and isolated (node) side of the two optocouplers while the other is nonisolated. The non-isolated regulator supplies the transceiver and the non-isolated (network) half of the two optocouplers.

Figure 19. Isolated node powered by the network.

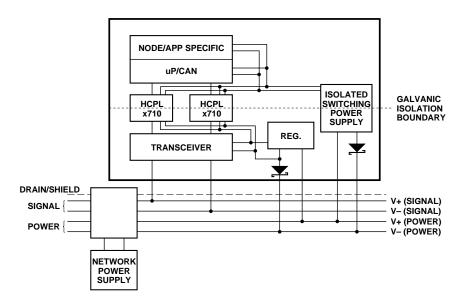

# Isolated Node with Transceiver Powered by the Network

Figure 20 shows a node powered by both the network and another source. In this case, the transceiver and isolated (network) side of the two optocouplers are powered by the network. The rest of the node is powered by the AC line which is very beneficial when an application requires a significant amount of power. This method is also desirable as it does not heavily load the network.

More importantly, the unique "dual-inverting" design of the HCPL-x710 ensure the network will not "lock-up" if either AC line

power to the node is lost or the node powered-off. Specifically, when input power  $(V_{DD1})$  to the HCPL-x710 located in the transmit path is eliminated, a RECESSIVE bus state is ensured as the HCPL-x710 output voltage  $(V_0)$  go HIGH.

### \*Bus V+ Sensing

It is suggested that the Bus V+ sense block shown in Figure 20 be implemented. A locally powered node with an un-powered isolated Physical Layer will accumulate errors and become bus-off if it attempts to transmit. The Bus V+ sense signal would be used to change the BOI attribute of the

DeviceNet Object to the "autoreset" (01) value. Refer to Volume 1, Section 5.5.3. This would cause the node to continually reset until bus power was detected. Once power was detected, the BOI attribute would be returned to the "hold in bus-off" (00) value. The BOI attribute should not be left in the "auto-reset" (01) value since this defeats the jabber protection capability of the CAN error confinement. Any inexpensive low frequency optical isolator can be used to implement this feature.

Figure 20. Isolated node with transceiver powered by the network.

# **Isolated Node Providing Power to** the Network

Figure 21 shows a node providing power to the network. The AC line powers a regulator which provides five (5) volts locally. The AC line also powers a 24 volt isolated supply, which powers the network, and another five-volt regulator, which, in turn, powers the transceiver and isolated

(network) side of the two optocouplers. This method is recommended when there are a limited number of devices on the network that don't require much power, thus eliminating the need for separate power supplies.

More importantly, the unique "dual-inverting" design of the HCPL-x710 ensure the network

will not "lock-up" if either AC line power to the node is lost or the node powered-off. Specifically, when input power  $(V_{\rm DD1})$  to the HCPL-x710 located in the transmit path is eliminated, a RECESSIVE bus state is ensured as the HCPL-x710 output voltage  $(V_0)$  go HIGH.

$\label{lem:figure 21.} \textbf{Isolated node providing power to the network}.$

### **Power Supplies and Bypassing**

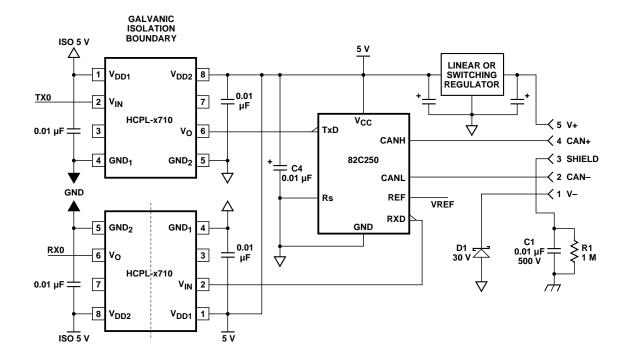

The recommended DeviceNet application circuit is shown in Figure 22. Since the HCPL-x710 are fully compatible with CMOS logic level signals, the optocoupler is connected directly to the CAN

transceiver. Two bypass capacitors (with values between 0.01 and 0.1  $\mu$ F) are required and should be located as close as possible to the input and output power-supply pins of the HCPL-x710. For each capacitor, the total

lead length between both ends of the capacitor and the power supply pins should not exceed 20 mm. The bypass capacitors are required because of the highspeed digital nature of the signals inside the optocoupler.

Figure 22. Recommended DeviceNet application circuit.

# Implementing PROFIBUS with the HCPL-x710

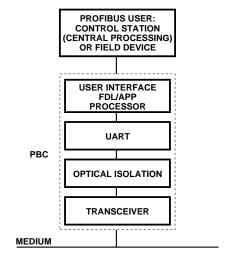

An acronym for Process Fieldbus, PROFIBUS is essentially a twisted-pair serial link very similar to RS-485 capable of achieving high-speed communication up to 12 MBd. As shown in Figure 23, a PROFIBUS Controller (PBC) establishes the connection of a field automation unit (control or central processing station) or a field device to the transmission medium. The PBC consists of the line transceiver, optical isolation, frame character transmitter/ receiver (UART), and the FDL/ APP processor with the interface to the PROFIBUS user.

Figure 23. PROFIBUS Controller (PBC).

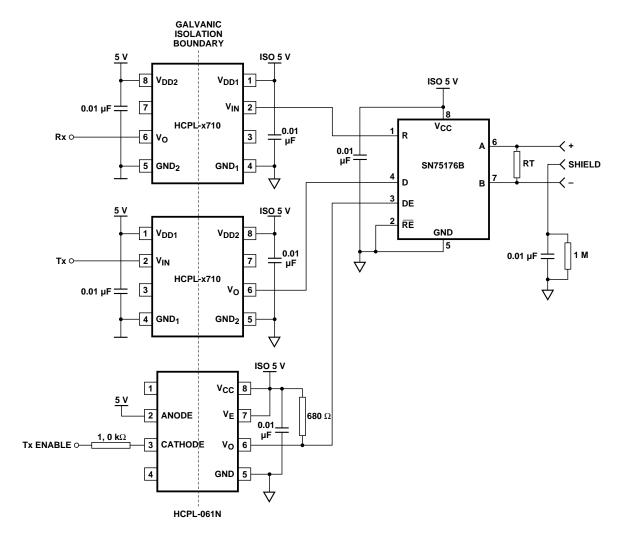

### **Power Supplies and Bypassing**

The recommended PROFIBUS application circuit is shown in Figure 24. Since the HCPL-x710 are fully compatible with CMOS logic level signals, the optocoupler is connected directly to the transceiver. Two bypass capacitors (with values between 0.01 and 0.1  $\mu F)$  are required and should be located as close as possible to the input and output power-supply pins of the HCPL-x710. For each capacitor,

the total lead length between both ends of the capacitor and the power supply pins should not exceed 20 mm. The bypass capacitors are required because of the high-speed digital nature of the signals inside the optocoupler.

Being very similar to multi-station RS485 systems, the HCPL-061N optocoupler provides a transmit disable function which is necessary to make the bus free after each master/slave transmission cycle. Specifically, the HCPL-061N disables the transmitter of the line driver by putting it into a high state mode. In addition, the HCPL-061N switches the RX/TX driver IC into the listen mode. The HCPL-061N offers HCMOS compatibility and the high CMR performance (1 kV/ $\mu$ s at V<sub>CM</sub> = 1000 V) essential in industrial communication interfaces.

Figure 24. Recommended PROFIBUS application circuit.

### www.agilent.com/semiconductors

For product information and a complete list of distributors, please go to our web site.

For technical assistance call:

Americas/Canada: +1 (800) 235-0312 or

(916) 788-6763

Europe: +49 (0) 6441 92460 China: 10800 650 0017 Hong Kong: (+65) 6756 2394

India, Australia, New Zealand: (+65) 6755 1939 Japan: (+81 3) 3335-8152 (Domestic/International), or 0120-61-1280 (Domestic Only)

Korea: (+65) 6755 1989

Singapore, Malaysia, Vietnam, Thailand, Philippines, Indonesia: (+65) 6755 2044

Taiwan: (+65) 6755 1843

Data subject to change.

Copyright © 2005 Agilent Technologies, Inc.

Obsoletes 5989-0789EN

February 28, 2005

5989-2134EN